클린룸 6개 배치…생산력 50% 이상 확대

HBM4·1c D램 '국내 생산 중심' 전략 강화

[서울=뉴스핌] 김정인 기자 = 삼성전자가 중단됐던 평택캠퍼스 5라인(P5) 건설을 2년 만에 재개하며 인공지능(AI) 시대 메모리 주도권 확보전에 본격적으로 나섰다. AI용 그래픽처리장치(GPU) 공급 확대와 함께 고대역폭메모리(HBM)4 수요가 빠르게 증가하는 상황에서, 2028년 가동을 목표로 한 P5는 차세대 HBM과 10나노급 6세대(1c) D램을 생산하는 핵심 거점으로 구축된다. 업계는 이번 결정이 중장기 시장 재편에 대응해 'HBM4 반격' 기반을 마련하려는 전략적 선택으로 보고 있다.

◆ 멈췄던 P5, 2년 만에 재가동…2028년 '메가 팹' 완성 목표

17일 업계에 따르면 삼성전자는 최근 임시 경영위원회를 열고 평택사업장 2단지 5라인의 골조 공사를 추진하기로 결정했다. 2022~2023년 반도체 업황 침체와 적자 부담 속에서 공사가 중단된 지 약 2년 만이다.

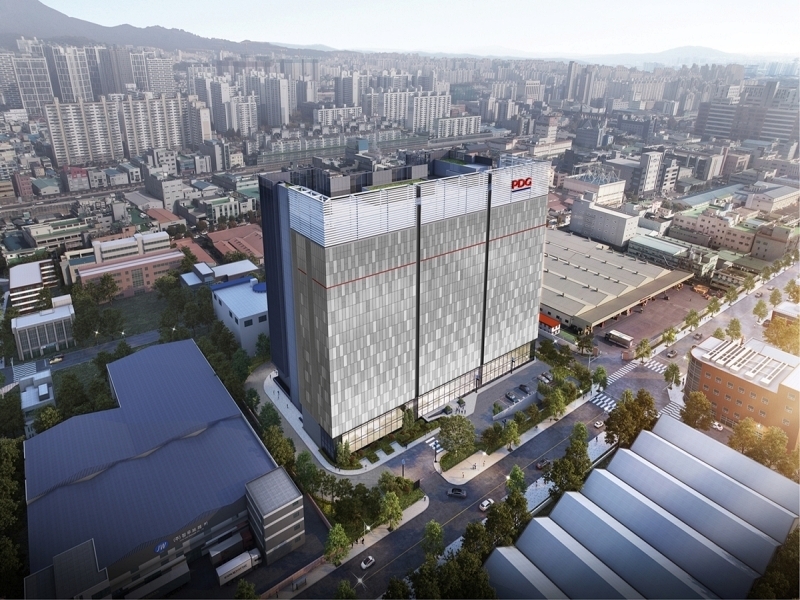

P5는 가로 650m, 세로 195m 규모의 3층 건물로 조성된다. 기존 라인(500×200m·2층)보다 면적과 층고가 모두 확대된 '메가 팹' 형태다. 공장 내부에 마련되는 클린룸은 총 6개로, 기존 4공장의 4개보다 크게 늘어난다.

클린룸은 반도체 생산 장비가 실제로 배치되는 초정밀·초청정 제조 공간으로, 개수가 늘어나면 투입 가능한 장비 수와 공정 라인이 함께 확대된다. 식각·증착·노광·세정 등 주요 공정 장비가 모두 이 공간 내부의 전용 구역에 설치되기 때문에, 클린룸의 수와 규모는 사실상 공장의 생산능력을 좌우하는 핵심 요소로 평가된다. 특히 4공장 대비 클린룸이 1.5배로 늘어나는 만큼, 업계는 전체 생산능력도 구조적으로 50% 이상 확대될 것으로 보고 있다.

삼성전자는 P5에서 10나노급 6세대(1c) D램과 차세대 HBM 생산을 추진하며, HBM4 목표 양산 시점인 내년 하반기 이후 필요한 물량의 핵심 공급기지 역할을 맡길 계획이다. 특히 엔비디아가 2030년까지 한국 정부 및 기업에 공급하기로 한 AI용 GPU 26만 장에 필요한 HBM4 상당량도 P5에서 생산될 것으로 전망된다.

◆ AI 수요 폭증 속 HBM4 '승부수'…삼성의 반격 기반

HBM3E까지는 SK하이닉스가 절대 우위를 보이고 있지만, HBM4부터는 인터페이스 구조와 공정 체계가 크게 바뀌면서 경쟁 구도가 재편되는 구간이다. 특히 HBM4는 4나노 파운드리 기반 로직 공정을 활용해 기존 대비 2배 향상된 전송 속도(11Gbps 이상)와 40% 개선된 전력 효율을 구현하는 것이 특징이다. 공정 난도가 높아지는 만큼 제조·패키징·인증 과정에서 기업 간 기술 격차가 다시 벌어질 수 있어, 업계는 HBM4가 '2라운드 경쟁'의 시작점이 될 것으로 보고 있다.

이 과정에서 삼성은 메모리·파운드리·첨단 패키징을 모두 갖춘 유일한 업체로, 생산라인의 물리적 인접성이 곧 경쟁력으로 직결된다. 실제 HBM의 핵심인 베이스다이가 로직 공정으로 이동하기 때문에 파운드리사업부의 역할도 커진다. 이에 업계는 P5가 향후 파운드리 설비 일부를 수용할 가능성도 높게 보고 있다.

삼성전자는 P5 양산 안정화와 함께 HBM4 수율·발열·인증 개선이 빠르게 이뤄질 경우, AI 메모리 시장에서 주도권 회복의 기반을 마련할 수 있을 것으로 기대하고 있다.

한편 P5가 완성되면 평택캠퍼스 상주 인력은 임직원·협력사 포함 10만명을 넘어설 전망이다. 삼성은 총 6개 공장까지 건립해 생산유발 550조 원, 고용 130만명 이상의 효과를 낼 것으로 보고 있으며, 투자 시점 조율에 따라 2030년 이전 조기 완공 가능성도 열어두고 있다.

◆ 용어 설명

HBM(High Bandwidth Memory): 고대역폭 메모리. GPU·AI 칩과 함께 사용되는 초고속 DRAM으로, 층층이 쌓아 올리는 '적층(3D TSV)' 기술 기반. AI 서버에서 필수.

1c DRAM (10나노급 6세대): 삼성의 10nm급 DRAM 공정 세대 명칭. 1a → 1b → 1c → 1d 순으로 발전. 1c는 밀도·속도·전력효율이 개선된 6세대 DRAM.

메가 팹(Mega Fab): 초대형 반도체 제조라인. 단순한 '공장'이 아니라, 대규모 전력·용수 인프라, 초대형 클린룸, 범위 수백 미터급의 건물로 구성.

베이스다이(Base Die): HBM의 가장 하단부 논리칩(로직칩). 메모리 스택 전체를 제어하는 핵심부. HBM4에서는 고성능 로직 공정으로 전환되어 중요도 증가.

TSV(Through-Silicon Via): 실리콘 웨이퍼를 수직으로 관통하는 전기적 연결 기술. HBM에서 메모리칩을 '층층이 쌓아 올릴 수 있게' 하는 핵심 기술.

kji01@newspim.com

![[단독] SK, 넥스트 반도체 '앵커기업' 된다](https://newsimg.sedaily.com/2025/11/17/2H0HNCZ7GA_2.png)

![[현대차그룹 국내 투자] ①2030년까지 사상 최대 규모 125.2조원 투입](https://img.newspim.com/news/2024/10/12/241012064054938.jpg)