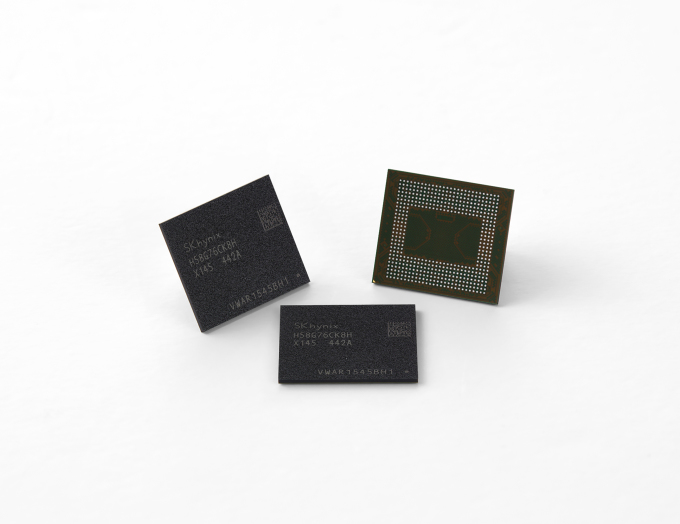

3D 낸드 플래시 기술은 저장용량 확대를 위해 셀을 수직으로 적층하는 구조로 진화해 왔다. 현재 상용 제품은 300단을 넘어섰으며, 업계는 2030년까지 1000단 이상을 실현하기 위한 기술 개발에 집중하고 있다. 그러나 셀 적층이 고도화될수록 공정 복잡도와 제조 원가는 물론, 셀 간 전기적 간섭과 데이터 유지 특성 저하 등 다양한 물리적 한계에 직면하고 있다.

특히 수직 방향으로 더 많은 셀을 집적하기 위해 산화막과 워드라인의 두께를 줄이는 'z피치 스케일링'은 핵심 기술로 평가된다. 하지만 이 방식은 게이트 길이 축소에 따른 채널 제어력 저하, 인접 셀 간 정전기적 간섭 증가, 저장 전하의 수평 방향 확산(lateral charge migration)과 같은 전기적 성능 저하를 야기할 수 있다. 이는 임계 전압 감소, 프로그램 및 삭제 전압 증가, 데이터 유지 특성 저하로 이어지며, 3D 낸드의 신뢰성과 수율 확보에 직접적인 영향을 준다.

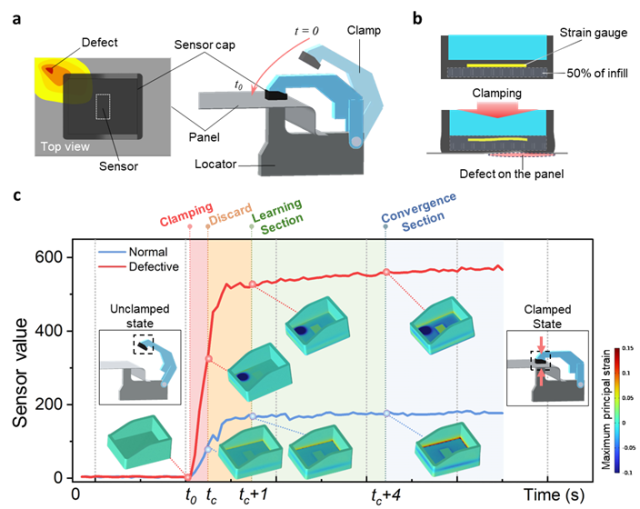

아이멕(imec)은 이러한 문제를 해결하기 위한 공정 기술로 '공기갭 통합'과 '전하 트랩층 분리(charge trap layer separation)' 기술을 개발하고 있다. 공기갭 통합은 워드라인 사이에 유전율이 낮은 공기층을 형성함으로써 셀 간 간섭을 줄이는 방식이다. 기존 2D 낸드 구조에서 유사한 기법이 적용된 바 있으나, 수십 마이크로미터 두께의 3D 적층 구조에서는 구현이 어렵다는 기술적 제약이 있었다. 아이멕은 메모리 홀 내부에서 산화막을 선택적으로 리세스하고, 산화막-질화막-산화막(ONO) 스택 증착 전 공기갭이 자가정렬 방식으로 형성되도록 하는 공정을 제시했다. 이 방식은 워드라인과의 정렬 정확도를 높이고, 대면적 제조에서의 확장성을 확보할 수 있다는 점에서 의의가 있다.

실험 결과, 공기갭이 적용된 셀은 그렇지 않은 셀에 비해 인접 셀에 패스 전압을 인가했을 때 임계 전압 변화가 작았다. 이는 전기적 간섭이 효과적으로 억제됐음을 시사한다. 또 프로그램/삭제 반복 동작 내구성에서도 기존 구조와 유사한 수준을 유지했다. 공기갭 통합 기술은 z피치 스케일링에 따른 전기적 성능 저하를 완화하는 현실적인 해법으로 검증됐다.

전하 트랩층 분리 기술은 수직으로 연속된 실리콘 나이트라이드(SiN) 기반의 층을 절단해, 저장 전하가 수평 방향으로 확산되는 것을 억제하는 방식이다. 시뮬레이션 분석 결과, 트랩층을 분리하면 메모리 윈도가 개선되고 데이터 유지 특성이 향상되는 효과가 나타났다. 다만, 깊고 좁은 메모리 홀 측벽을 따라 정밀한 방향성 식각과 증착을 수행해야 하는 만큼, 공정 구현 난도가 높은 기술로 분류된다. 아이멕은 장비 업체들과 협력해 해당 구조를 실제 공정에 적용하기 위한 기술 개발을 진행 중이다.

공기갭 통합과 전하 트랩층 분리 기술은 상호 보완적인 특성을 가진다. 두 기술을 함께 적용하면 셀 간 간섭과 전하 확산이라는 z피치 스케일링의 두 가지 주요 전기적 문제를 동시에 해결할 수 있다. 이를 통해 1000단 이상의 고적층 구조에서도 성능과 신뢰성을 유지할 수 있는 기반이 마련된다. 단순히 층 수를 늘리는 접근을 넘어서, 전기적 제약을 극복하는 방향으로의 기술 전환이 요구되고 있다.

고집적 3D 낸드 기술은 향후 클라우드, 인공지능(AI), 엣지 디바이스 등에서 급증하는 대용량 데이터 처리 수요에 대응하기 위한 핵심 인프라로 자리 잡을 것이다. 아이멕은 공정, 구조, 재료 전반에서의 혁신을 통해 차세대 메모리 기술의 물리적 한계를 해결하고, 산업 전반의 기술적 기반을 뒷받침하는 데 집중하고 있다.

마르턴 로스뮐런 스토리지 메모리 프로그램 디렉터 maarten.rosmeulen@imec.be

![[나노 혁신, 미래를 설계하다] 〈8〉 '반백년' 상보, 나노코팅 기술로 100년 기업 도약](https://img.etnews.com/news/article/2025/09/02/news-p.v1.20250902.48f1e1fb996d455798a3f2cdb5fbd1e2_P1.jpg)

![[IR핌] 캠시스, 신사업 'AI카메라·IoT 태그' 추진…"초도 물량 본격화"](https://img.newspim.com/news/2025/09/01/2509011432482640_w.jpg)